# An Instruction Manual on Basic Electronics

**Network of Instrument Technical personnel** and User scientists of Bangladesh (NITUB)

## An Instruction Manual on

# Basic Electronics

## Author

**Dr. Md. Habibur Rahman** Professor Department of Electrical & Electronic Engineering University of Dhaka Dhaka-1000, Bangladesh

#### Reviewer

Dr. Rezaul Karim Mazumder Former Professor Department of Electrical & Electronic Engineering University of Dhaka Dhaka-1000, Bangladesh

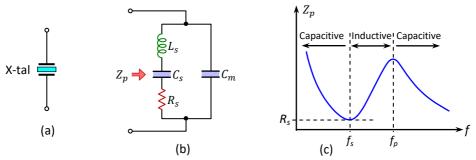

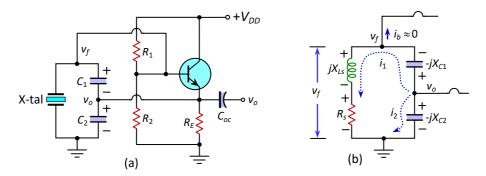

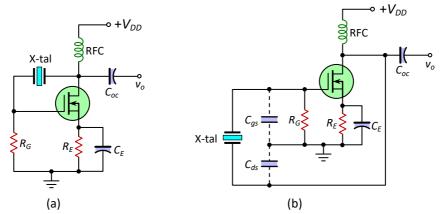

#### Sponsor

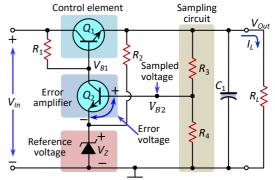

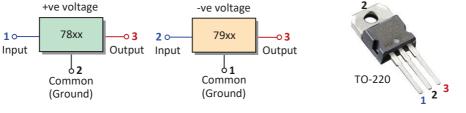

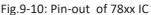

International Science Programme (ISP) Uppsala University, Sweden

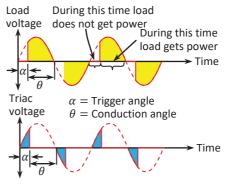

#### **Published by**

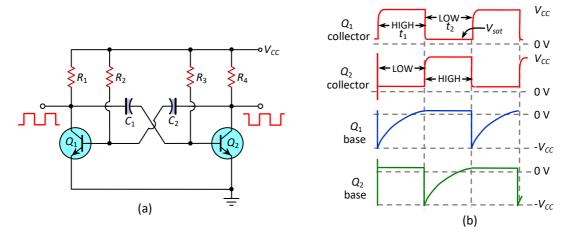

Network of Instrument Technical personnel and User scientists of Bangladesh (NITUB)

#### **Printed by**

**DS Printing and Packaging** 243/D New Elephant Road, Dhaka E-mail: adspp016@gmail.com

## Contents

| Chapter 1  | Basic Concepts for Electronics    | 5   |

|------------|-----------------------------------|-----|

| Chapter 2  | PN Junction Diodes                | 19  |

| Chapter 3  | Bipolar Junction Transistor (BJT) | 39  |

| Chapter 4  | Field Effect Transistor (FET)     | 61  |

| Chapter 5  | Feedback in Amplifiers            | 73  |

| Chapter 6  | <b>Operational Amplifiers</b>     | 77  |

| Chapter 7  | Power Amplifiers                  | 83  |

| Chapter 8  | Oscillators                       | 89  |

| Chapter 9  | Regulated Power Supply            | 103 |

| Chapter 10 | Power Electronics                 | 109 |

| Chapter 11 | Digital Electronics               | 113 |

|            |                                   |     |

## **Basic Concepts for Electronics**

## 1.1 Introduction

Currently, we people live in an era of developed engineering and technology mainly Electrical and Electronics Engineering. In today's world, people cannot think of their lives without mobile phone, television, computer and other devices that have made our lives easy and enjoyable. These devices are the gift of Electrical and Electronics Engineering. All of them work based on the flow of charges. As this souvenir is made for non electrical engineers, before going to the main topics, it is necessary to explain some terms related to electrical and electronic circuits. A circuit is a complete path through which charge flows. Professionals of different fields study electronics. The prerequisites to study electronics are DC/AC circuit courses, Electricity and magnetism, algebra, and some trigonometry. Basic Electronics provides understanding of construction, operation, testing of semiconductor devices and the circuits in which they are used. As the targeted readers of this Manual are not directly from electrical fields, we will discuss some important concepts necessary to understand electronics.

### 1.2 Symbols Used in Electronics

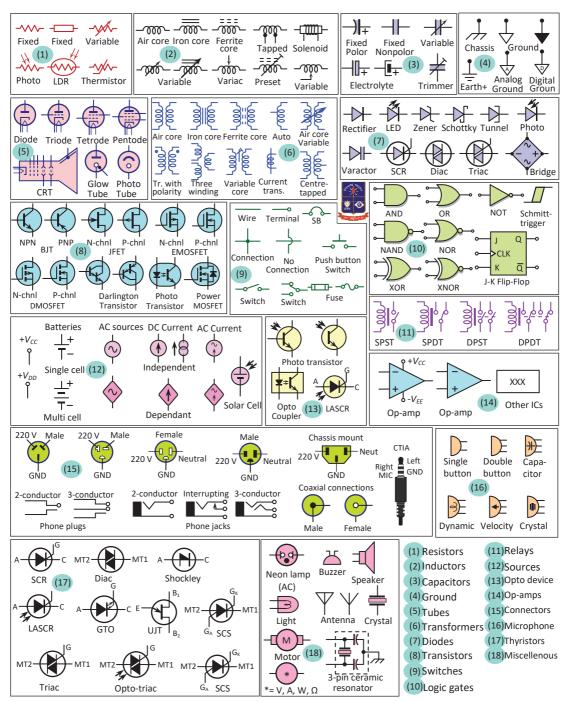

The electronic circuits are constructed using semiconductor devices, power sources, switches etc. In schematic diagrams of circuits, all these components are represented by their symbols. Some very common symbols are given in Fig.1-1. Although, we do not require memorizing all of them, we can use them if required for further studies/applications.

Common Symbols Used in Electrical and Electronics Circuits

Fig.1-1: Symbols of some common components used in electronics

### 1.3 Electric Potential and Current

Any materials are made of atoms and atoms are made of electrons (negative charge), proton (positive charge) and neutron (chargeless). Normally, atoms possess equal number of electrons and

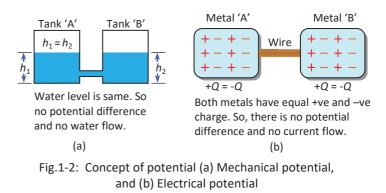

protons. For this reason, any materials, like gold (Au), silver (Ag) copper (Cu), aluminum (Al) etc., have equal amount of positive charge and negative charge. As a result, normally each material is electrically neutral and has no potential difference. The situation is depicted in Fig.1-2 using water tank analogy. In Fig.1-2(a), there are two water tanks connected by a pipe.

As the water levels are same in both the tanks, there is no potential (mechanical) difference, and hence, no flow of water. Similarly, in Fig.1-2(b), there are two metals, connected by a conducting wire. As the metals have equal number of positive and negative charges, so, there is no potential difference between them. Hence, there is no flow of charges or current.

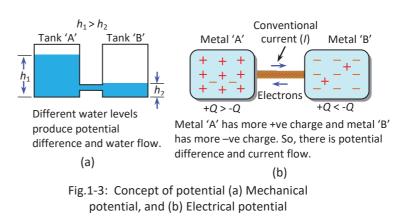

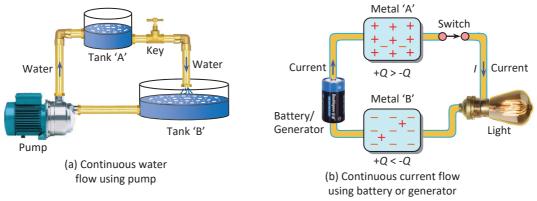

But as shown in Fig.1-3(a), the water level in tank 'A' is higher than that in tank 'B'. So, there will have a mechanical potential difference, and hence, water will flow from tank 'A' to tank 'B' (higher potential to lower potential). Similarly, by any mechanism, if the positive charges and negative charges of metal 'A' and 'B' of Fig.1-3(b) are separated, there exists a potential difference. As shown in Fig.1-3(b), metal 'A' is at higher potential (higher positive charges) compared to metal 'B'. Therefore, positive charges will flow from metal 'A' to metal 'B' (actually electrons flow in opposite direction).

Potential difference tells us how much electrical energy is available to push electric charges through a circuit. The unit to measure electric potential difference is volt (V). Electric potential

difference is also referred to as simply *voltage*. Potential difference (or voltage) is measured by an instrument called *Voltmeter*. It is always connected in parallel to the points where potential difference is to be measured as given in Fig.1-21(a).

As shown in Fig.1-3(a), due to the potential difference between tank 'A' and 'B',

water will flow through the pipe connecting them. Similarly, due to the potential difference between metals 'A' and 'B', electric charge will flow from 'A' to 'B'. As positive charge cannot move, electrons will flow from metal 'B' to metal 'A' [Fig.1-3(b)]. The flow of charge will stop when the potential difference is zero. This flow of charge is called the *current*. Actually the rate at which the electric charges flow through a device is called current. The unit used to measure the current is called *Ampere* (A). 1 ampere is equivalent to a flow of 1 Coulomb per second through the cross-section of a conductor or device. Although current was originally thought to be a flow of positive charge, we now know that in most cases it is the flow of electrons. The direction of conventional current is just opposite to the direction of electrons flow. The instrument used to measure the current is *ammeter*. Unlike the voltmeter, ammeter is connected in series, so that, the full current can flow through the meter as shown in Fig.1-21(b).

Fig.1-4: Continuous flow of water and current with the help of external energy source

As shown in Fig.1-4(a), if we want continuous flow of water, we have to use a pump that will maintain the potential difference. Similarly, to get continuous current, we must use some source of electrical energy (battery or generator). The *friction* of the pipe that opposes the flow of water is analogous to the *resistance* in electrical circuit that opposes the flow of current.

## 1.4 AC and DC Currents

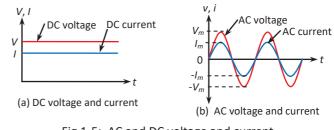

There are two types of voltage and current. These are: 1) *DC voltage* and *current*, 2) *AC voltage* and *current*. The examples of DC voltage sources are dry cell batteries, lead-acid batteries, DC power supply etc. The main property of these sources is that the voltage and current do not change with time (do not alternate). Fig.1-5(a) shows the graphs of DC voltage and DC current.

The voltage produced by a generator is AC. The power coming from grid-line in our house is the example of AC voltage and current. The main property of these sources is that the voltage and current change with time (alternate). Fig.1-5(b) shows the graphs of AC voltage and AC current. The DC voltage and current is represented by their

Fig.1-5: AC and DC voltage and current

values only, whereas, the AC voltage and current are represented by their RMS (root-mean-square) values and frequency. In Bangladesh, the grid power used in households has 220 V (RMS) and 50 Hz.

## 1.5 Three Elements of Circuits (RLC)

A circuit is a complete path through which electric charge travels on. A simple circuit contains three components necessary to have electric activity, namely, *sources of voltage, conductive paths*, and *resistors.* In addition to resistors, electrical circuits may use two more components, these are *capacitors* and *inductors*. A brief discussion on these elements is given here.

### Resistors

Although any conducting wire of circuits produces unwanted resistance to the flow of current, we always add some resistance in circuits to control the current. The component that produces this resistance is called a *resistor*. A resistor is a passive two-terminal electrical component that provides resistance (opposition) to the flow of charges. The ability of a resistor to resist the current is called *resistance* and is denoted by R.

In electronic circuits, resistors are used to reduce current flow, adjust signal levels, to divide voltages, and bias active elements (like diodes and transistors). Resistance of a conducting wire is given by

$$R = \rho \frac{l}{A} \tag{1-1}$$

where,  $\rho$  is the resistivity of the material of the wire, l is the length of the wire, and A is its crosssectional area. Different materials have different values of  $\rho$ . Silver has the lowest value of  $\rho$ .

To construct circuits, resistors of different values and shapes are used. Different resistors have different resistance and power rating. Some of the resistors commercially available in the market are shown in Fig.1-6.

Fig.1-6: Photographs of different fixed and variable resistors

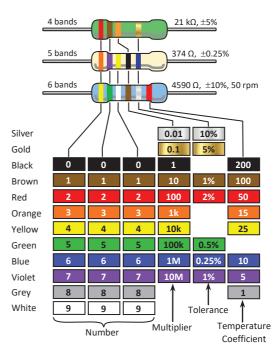

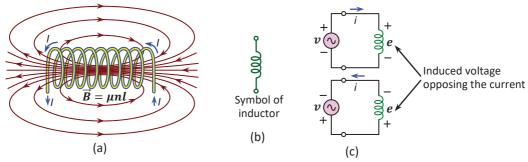

## **Color Code Marking of Leaded Resistors**

The value of resistance of a resistor is written on it using different colors called *color code*. The resistance color code consists of three or four color bands and is followed by a band representing the tolerance (variation of resistance). Another color is sometimes used

which is the temperature coefficient band. If provided, it is to the right of the tolerance band.

In the resistance color codes, the first two or three colors give the significant figures of the resistance value (in ohms), followed by a multiplier color. This is a factor by which the significant figure must be multiplied (i.e. the number of zeros to be added after the significant figures) to find the actual resistance value. The next color is the tolerance of the resistance. The tolerance of a resistor is the maximum difference between its actual value and the written value. For example, the actual value of a  $1k\Omega \pm 20\%$  resistor may have any value between  $800 \Omega$  to  $1200 \Omega$ . The color to the right of tolerance band (if any) is the temperature coefficient of resistance (TCR). TCR tells how much resistance changes as its temperature changes. It is usually expressed in ppm/°C (parts per million per degree Celsius) units.

As shown in Fig.1-7, the colors on a resistor represent a number (decimal digit). We can remember these numbers using a popular sentence: "B B ROY Good Boy Very Good Worker" (Fig.1-8). First "B" is black and its value is "0" and the second "B" is brown = "1".

Fig.1-17: Process to read color codes of resistors

| В                                              | B | RC | )Y | Good | Boy | Very | Good | Worker |  |

|------------------------------------------------|---|----|----|------|-----|------|------|--------|--|

| 0                                              | 1 | 23 | 4  | 5    | 6   | 7    | 8    | 9      |  |

| Fig.1-8.: Process to memorize values of colors |   |    |    |      |     |      |      |        |  |

#### Example 1.1

Determine the resistance value of the resistor shown in Fig.1-9.

#### Solution:

Here, the first three colors are Red(2)-Violet(7)-Yellow(4). So the significant figure will be 274. The multiplier color is Gold=0.1, and the tolerance is Brown=1%. Therefore, the value of this resistor will be  $274 \times 0.1 \pm 1\% = 27.4 \Omega \pm 1\%$ . Moreover, the Red color on the rightmost position represents 50 ppm/°C TCR.

**Comments**: 50 ppm/°C TCR means, its resistance will not change more than 0.00005 ohms (50/1,000,000) per ohm per degree Celsius temperature change (within the rated temperature range of -55 to +145°C, measured from 25°C room temperature.)

Fig.1-9: Resistor for Example 1.1

## 1.6 Capacitors and Capacitance

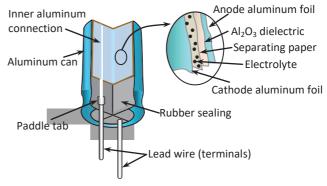

A capacitor (originally called condenser) is a passive two-terminal electrical component used to store electrostatic energy. Though the shapes and sizes of practical capacitors vary widely

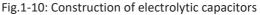

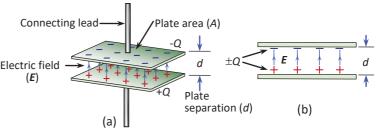

(Fig.1-14), but all capacitors contain two electrical conducting plates separated by a dielectric (i.e., insulator). The conductors can be thin films of metal, aluminum foil (rolled cylindrically) or disks, etc. (Fig.1-10 and 11). Capacitors are widely used as parts of electrical circuits in many common electrical devices. Unlike а resistor. а capacitor does not dissipate energy. Instead, a capacitor stores energy in the form of electrostatic field between its plates.

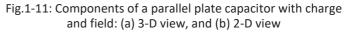

When potential difference is applied across a capacitor, negative charge accumulates on one palate and positive charge on the other plate as shown in Fig.1-11. Due to these opposite charges between the dielectric film. an electric field is developed. The ability of a capacitor to store charge is called capacitance and is denoted by C. The SI unit of capacitance is Farad (F), which is equal to one coulomb per volt (1 C/V). The capacitance of a capacitor will be 1 F, if the capacitor can store 1 Coulomb 1 V charge for potential difference applied to its plates. Farad is a very large unit, so the practical unit of capacitance is microfarad ( $1\mu F = 10^{-6}F$ ).

Fig.1-12: Values are written in different ways on capacitors

In practice, the dielectric between the plates has an electric field strength limit, known as the *breakdown voltage*. This voltage is called the *tolerance voltage* of the capacitor. In some

capacitors (e.g. electrolytic capacitors), the tolerance voltage is written on the capacitor [Fig.1-12(a)]. The applied voltage to a capacitor must be equal or less than the tolerance voltage.

In non-polar capacitors (ceramic, miller, tantalum etc.) the value of the capacitance is either written as a code number (Fig.1-12) or using colors. In coding system, the first 2 digits give the value and the 3<sup>rd</sup> digit is the multiplier, that is used as a power of 10 and the value will be in pico-Farad (pF). For example, the code number written on a ceramic capacitor is 203 [Fig.1-12(b)]. Its value will be  $20 \times 10^3$  pF = 20000 pF = 0.02 µF or 20 nF.

Capacitors are widely used in electronic circuits for blocking direct current while allowing alternating current to pass. In analog filter networks, they smooth the output of power supplies. In resonant circuits they tune radios to particular frequencies. In electric power transmission systems they stabilize voltage and power flow.

Already we have discussed that a capacitor can store charge. In DC (direct current) circuits capacitors store charges, but in AC circuits capacitors work just like a resistor. The opposition produced by a capacitor to the AC current is called *capacitive reactance* and is denoted by  $X_c$ . The reactance of a capacitor is inversely proportional to its capacitance and the frequency of the AC current. Mathematically,

$$X_C = \frac{1}{\omega C} = \frac{1}{2\pi f C} \tag{1-2}$$

where, f is the frequency of AC current and C is the capacitance of the capacitor.

For AC voltage, the capacitor behaves as a linear device, i.e., if the frequency and the capacitance are constant, the capacitor current will increase linearly with the increase in AC voltage.

#### Example 1-2

Determine the value of capacitance of the capacitor shown in Fig.1-13. Calculate the value of reactance  $(X_C)$  if the capacitor is used for 50 Hz AC voltage.

#### Solution:

Fig.1-13: Ceramic capacitor for Example 1-2

The code number written on the capacitor is 104. So, the value of capacitance will be  $10 \times 10^4 \text{ pF} = 100000 \text{ pF} = 0.1 \text{ }\mu\text{F}$  or 100 nF. The reactance can be calculated using Equ.(1-2).

$$X_C = \frac{1}{2\pi fC} = \frac{1}{2\pi (50 \text{ Hz})(0.1 \times 10^{-6})} \approx 32 \text{ k}\Omega \text{ [Ans.]}$$

**Comments**: In Bangladesh, the frequency of AC supply voltage is 50 Hz. Hence, here we have considered f = 50 Hz.

The shapes and sizes of practical capacitors vary widely according to their applications. A number of capacitors are available in markets. Some of the common capacitors are shown in Fig.1-14.

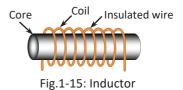

### **1.7 Inductors**

*Inductor* (also called coil, choke, or reactor) is a passive two-terminal electrical component that stores energy in magnetic field when electric current flows through them. An inductor typically consists of an insulated wire, wound into a coil around a core (Fig.1-15). When current flows through an inductor magnetic field is produced inside the coil as shown in Fig.1-16(a). If the current flowing through the inductor changes with time,

magnetic field also varies with time, and this time-varying magnetic field induces an electromotive force or voltage ( $\epsilon = -Ndi/dt$ ) across the inductor as described by Faraday's law of electromagnetic induction [Fig.1-16(c)]. According to Lenz's law, the induced voltage has such a polarity (direction) that it opposes the change in current that produces it. As a

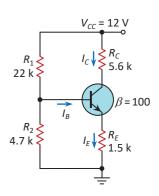

result, inductors oppose any change in current (AC current) through them by inducing a voltage (in opposite direction). The ability of an inductor to oppose the AC current is measured by a parameter called *inductance* and is denoted by *L*. Inductance is defined as the ratio of the induced voltage to the rate of change of current (L = e/(di/dt)). In the SI system, the unit of inductance is *Henry* (H). Along with capacitor and resistor, inductor is one of the three passive linear circuit elements that make up electrical and electronic circuits.

Fig.1-16: Inductor: (a) Coil with magnetic field, (b) Symbol of inductor, and (c) Inductors with induced voltage

Inductors are widely used in alternating current (AC), electronic equipment, particularly in radio equipment. They are used to block AC while allowing DC to pass. Unlike the capacitors, inductors oppose the AC current flowing through them. The opposing parameter of an inductor to AC current is called *inductive reactance* ( $X_L$ ) and is given by,

$$X_L = \omega L = 2\pi f L \tag{1-3}$$

The value of inductance is written directly on the device or using color code. Although, there is variation in number of colors, a 4-band color code system is shown in Fig.1-17.

There are various types of inductors available in the market with different values, sizes and shapes. To be familiar with them, photographs of some common inductors are given in Fig.1-18.

Fig.1-17: Process to read color codes of inductor

Fig.1-18: Photographs of various inductors available in market

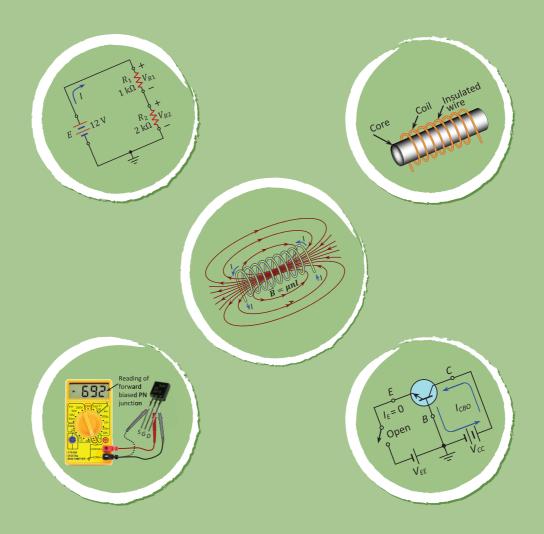

## 1.8 Use of Multimeter

A *multimeter* is an electronic (or electrical) instrument that is used to measure voltage, current, resistance etc. Actually a multimeter is a combination of *voltmeter, ammeter, and ohmmeter* and so on. Being a versatile instrument, it is most commonly used for measuring different components (resistors, inductors, capacitors, diodes, transistors etc.) and parameters (voltage, current, power etc.) of electronic (and electrical) circuits. It is also used for continuity testing

)

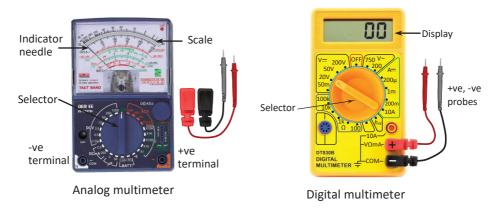

Fig.1-19: Analog and digital multimeters

purpose in servicing electrical and electronic circuits. There are mainly two types of multimeters: (1) *Analog multimeter*, and (2) *Digital multimeter*. The photographs of an analog and a digital multimeter are shown in Fig.1-19.

The main difference between them is. the analog multimeter has an indicating needle that moves on a scale to indicate the value of the measured parameter. On the other hand, the digital multimeter has a display unit, that directly shows the value (numerically) of the measured parameter. Both multimeters have a selector that has to be set to position appropriate (type of parameter and values) before using. We have to be careful to use these meters. The selector has to be set such a range that is greater than the

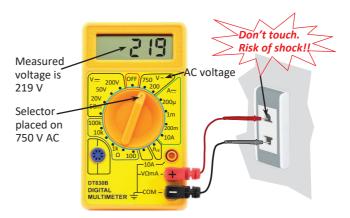

Fig.1-20: Digital multimeter measuring line voltage

value to be measured. For example if we want to measure line voltage using digital multimeter, the selector has to be set in the voltage range 750 VAC. Fig.1-20 shows how to measure the supply voltage in our house using a digital multimeter. As there is risk of shock, we must not touch the metallic portion of the meter probes.

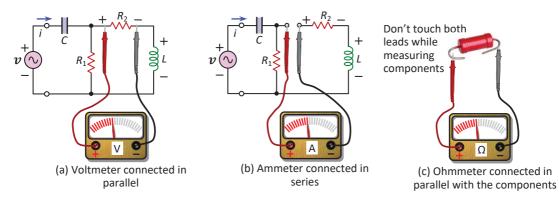

Measuring process of different parameters and elements are shown in Fig.1-21. To measure voltage the voltmeter has to be connected across two points or across the components [Fig.1-21(a)]. To measure current the meter has to be connected in series, that is, the current measuring point has to be opened and then connect the ammeter [Fig.1-21(b)]. Moreover, to measure resistance, capacitance, inductance etc. the meter has to be connected in parallel to those components [as shown in Fig.1-21(c)]. As human body has a finite resistance, we should not hold the components' both terminals by hand (holding one terminal is OK) while measuring

these components. If we hold both terminals, our body resistance will work in parallel to the measured components, so the reading may not be accurate.

Fig.1-21: Meter connection methods: (a) Voltage measurement, (b) Current measurement, and (c) Components measurement

## 1.9 Different Laws used in Electronics

#### **Ohm's Law**

Ohm's law gives the relationship between electric current and potential difference. The current that flows through a conductor (or resistor) is directly proportional to the potential difference (voltage) applied to it. Georg Simon Ohm, a German physicist was the first to state this law.

Ohm expressed his discovery in the form of a simple equation, describing how voltage, current, and resistance are interrelated:

Ohm's law equation

$$V = IR \tag{1-4}$$

In this algebraic expression, voltage (V) is equal to current (I) multiplied by resistance (R). Using algebra, we can manipulate this equation into two other variations to measure current (I) and resistance (R) as:

$$I = V/R \tag{1-5}$$

$$R = V/I \tag{1-6}$$

Using these equations we can calculate the value of any one parameter if the other two are known.

Let's see how these equations are used to analyze simple circuits.

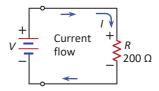

In the circuit of Fig.1-22, there is only one source of voltage (the battery) and only one source of resistance (R) to current. The value of current can easily be calculated using Ohm's Law. Let the applied voltage be 12 V and the resistance be 200  $\Omega$ . Therefore, the current flowing through this circuit will be,

Fig.1-22: Ohm's law applied to a simple circuit

$$I = \frac{V}{R} = \frac{12 \text{ V}}{200 \Omega} = 0.06 \text{ A} = 60 \text{ mA}$$

If we know the values of V, and I we can determine the value of the resistance as

$$R = \frac{V}{I} = \frac{12 \text{ V}}{60 \text{ mA}} = \frac{12 \text{ V}}{60 \text{ mA} \times 10^{-3}} = 200 \text{ }\Omega$$

If we know the values of *I*, and *R*, we can determine the voltage of the battery as,

$$V = IR = 60 \text{ mA} \times 10^{-3} \times 200 \Omega = 12 \text{ V}.$$

#### **Kirchhoff's Laws**

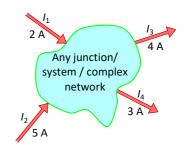

Kirchhoff's laws quantify how current flows through a circuit and how voltage varies around a loop in a circuit. *Kirchhoff's current law* (KCL) states that the algebraic sum of the currents entering and leaving an area, system,

or junction is zero. In other words, the sum of the

currents entering an area, system, or junction must equal the sum of the currents leaving the area, system, or junction.

In Fig.1-23, for instance, the shaded area can enclose an entire system, a complex network, or simply a junction of two or more electrical paths. In each case, the current entering must equal the current leaving. That is,

or,

$$I_1 + I_2 + (-I_3) + (-I_4) = 0$$

$I_1 + I_2 = I_3 + I_4$

or.

$2A + 5A = 4A + 3A$

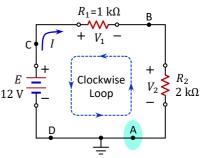

*Kirchhoff's voltage law* (KVL) states that the algebraic sum of the potential rises and drops around a closed loop (or path) is zero. A closed loop is any continuous electrical path that leaves

a point in one direction and returns to that same point from another direction without leaving the circuit. In Fig.1-24, by following the current, we can trace a continuous path that leaves point 'A' through  $R_2$  and returns to the same point through *E* without leaving the circuit. Therefore, ABCDA is a closed loop or path. We can apply KVL considering the loop in clockwise direction or counterclockwise direction. The result will be exactly same. To apply KVL properly, we must know the polarities of voltage drops. The terminal of a resistor into which the

Fig.1-24: KVL applied to a simple circuit

conventional current enter will be positive (+) and the terminal from where the conventional current leaves will be negative (-). '+' means higher potential and '-' means lower potential. So, there must have a potential difference across the resistor (between '+' and '-' sign). In applying KVL around a loop, if we move from '+' to '-', the potential difference will be negative, and if we move from '-' to '+', the potential difference will be positive.

Fig.1-23: KCL applied to a simple circuit

So, applying KVL in the loop of Fig.1-24, we can write,

$+V_2 + V_1 - E = 0$  $+IR_2 + IR_1 - E = 0$

Or using Ohm's law,

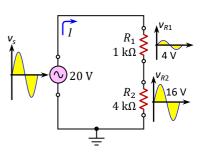

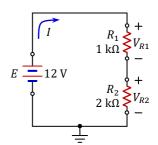

#### **Voltage Divider Rule**

*Voltage divider rule* is a method by which a voltage in a series circuit can be determined without calculating the current in the circuit. The voltage divider rule states that the voltage across a resistor in a series circuit is equal to the value of that resistor times the total applied voltage across the series elements divided by the sum of the series resistances.

Applying voltage divider rule we can easily calculate the voltage across the resistors of Fig.1-25 as,

$$V_{R1} = E \times \frac{R_1}{R_1 + R_2} = 12 \text{ V} \times \frac{1 \text{ k}}{1 \text{ k} + 2 \text{ k}} = 4 \text{ V}$$

$$V_{R2} = E \times \frac{R_2}{R_1 + R_2} = 12 \text{ V} \times \frac{2 \text{ k}}{1 \text{ k} + 2 \text{ k}} = 8 \text{ V}$$

and,

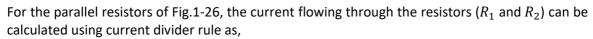

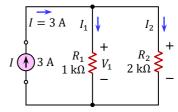

#### The Current Divider Rule

Current divider rule is used in parallel circuits (or elements). For parallel elements of different values, the current will split with a ratio equal to the inverse of their resistance values.

$$I_1 = I \times \frac{R_2}{R_1 + R_2} = 3 \text{ A} \times \frac{2 \text{ k}}{1 \text{ k} + 2 \text{ k}} = 2 \text{ A}$$

$$I_2 = I \times \frac{R_1}{R_1 + R_2} = 3 \text{ A} \times \frac{1 \text{ k}}{1 \text{ k} + 2 \text{ k}} = 1 \text{ A}$$

and,

**Note:** The laws and the rules, discussed so far, are also applicable for AC voltage. For circuits constructed using only resistors, the laws and the rules can be directly used as described above. However, if the circuit contains capacitor and/or inductor then we have to use the reactances of these components. Moreover, there will have a phase difference between the voltage and current due to the effect of capacitors and inductors.

Fig.1-27: Voltage divider rule used for AC voltage

Fig.1-25: Voltage divider rule applied to a simple circuit

Fig.1-26: Current divider rule applied to a simple circuit

## **PN** Junction Diodes

#### 2.1 Introduction

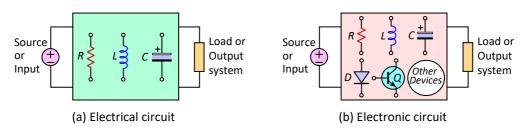

In *Basic Electronics* course, various types of devices and circuits are discussed. In the past, electronic circuits were constructed using vacuum tubes. The simplest vacuum tube, the diode, was invented in 1904. In 1947, Bardeen and Brattain at Bell Laboratories in the US invented the point-contact transistor, and in 1948 Shockley invented the junction transistor. Since then, new semiconductor devices have been invented and used in constructing electronic circuits. Already we know that a complete conducting path of charge flow is called a circuit. There are two types of circuits - electrical circuits and electronic circuits.

**Electrical Circuits:** An *electrical circuit* is a complete path in which, charge (i.e. electrons) flows from a voltage or current source. This type of circuit consists of three elements – resistors, capacitors and inductors but no semiconductor device or vacuum tube (Fig.2-1). They have no processing capability of signals.

**Electronic Circuits:** An electronic circuit is also a complete path in which charge (i.e. electrons) flows from a voltage or current source, but here, they have processing capability of signals. That is, electronic circuits can amplify, rectify or attenuate a signal and so on. Electronic circuits are also consisting of resistor, capacitor and inductor, but they must have at least one vacuum tube or semiconductor device- like a diode, a transistor etc.

Fig.2-1: Electrical and Electronic circuits

## 2.2 Insulator Conductor and Semiconductor

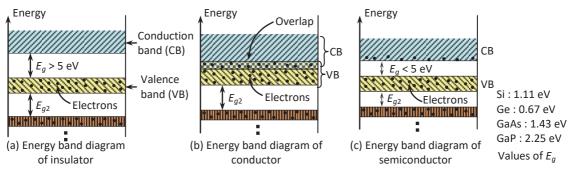

In any materials the maximum energy of an electron may be that of the valence electrons. That is, electrons can exist at most in the valence band (outermost bands). The difference between the conduction band (energy band of free electrons) and the valence band is called *Energy gap*  $(E_g)$ . Current carrying capacity of a material depends on the value of  $E_g$ . Depending on the current carrying capacity materials are divided into three categories as described below.

### **Insulators**

The materials that cannot carry electricity (flow of charge) are called *insulators*. The energy gaps  $(E_g)$  of these materials are very high so no electrons can get sufficient energy from external sources to go to the conduction band [Fig.2-2(a)]. Generally, the values of  $E_g$  of insulators are greater than 5 eV (electron-volt). Examples of insulators are rubbers, plastic, wood, cloths etc. Rubbers and plastics are used as insulating cover of electrical wire.

### Conductors

The materials that can carry electrical current easily are called *conductors*. In these materials, there is no energy gap between the conduction band and the valence band. In fact, there is an overlap between the conduction band and the valence band [Fig.2-2(b)]. For the overlap of the bands, some electrons of the valence band also possess the energy of the conduction band. These electrons behave as free electrons and can carry electrical current easily. Examples of conductors are silver, gold, copper, aluminum etc. The conductivity order of some common materials are: silver (Ag) > copper (Cu) > gold (Au) > aluminum (Al) > zinc (Zn) > nickel (Ni) > brass > bronze > iron (Fe).

#### Semiconductor

In between conductors and insulators, there are some materials called *semiconductors*. They are neither good conductor nor insulator. The materials with  $E_g < 5$  eV are called semiconductors [Fig.2-2(c)]. At absolute zero temperature, the conduction bands of these materials are completely empty, i.e., they have no free electrons. But at room temperature, some electrons of valence band can gain sufficient energy to jump to the conduction band. Thus, at room temperature they can carry electricity, but their resistivity is high compared to that of conductors. Examples of semiconductors are: silicon (Si), germanium (Ge), boron (B), phosphorus (P) etc. At room temperature, the values of energy gaps of some common semiconductors are given in Fig.2-2(c).

Fig.2-2: Energy band diagrams of different materials

Semiconductor materials are divided into two categories. These are *intrinsic* semiconductor and *extrinsic* semiconductor.

## 2.3 Intrinsic Semiconductor

Semiconductor in its purest form is called *intrinsic* semiconductor. Semiconductors used for different purpose have different purity levels. Metallurgical-grade semiconductor has the purity level of 98-99%, whereas the purity level of electronic-grade semiconductor is as high as 99.9999%. At room temperature some electrons can absorb sufficient amount of thermal energy to move to the conduction band leaving behind a vacancies of electrons in the valence band which are called *holes*. So, an intrinsic semiconductor has some free electrons in the conduction band and an equal number of holes in the valence band. At room temperature (300 K), the intrinsic carrier concentration (electrons,  $n_i$  and holes  $p_i$ ) per cubic centimeter is  $1.5 \times 10^{10}$  for silicon,  $2.4 \times 10^{13}$  for germanium and  $2.1 \times 10^6$  for gallium-arsenide. On the other hand, Cu contains  $8.4 \times 10^{22}$  free charge carriers (electrons) per cubic centimeter. For intrinsic semiconductor  $n_i = p_i$ .

### 2.4 Extrinsic semiconductor

A semiconductor when mixed with some impurity is called *extrinsic* semiconductor. The process of mixing impurity is called *doping* and the impurity itself is called *dopant* atom. The order of mixed impurity is 1 to 100 ppm (part per million). These mixed impurity atoms produce some additional energy levels in the energy gap of the semiconductor and hence decrease the energy gap. Now, at room temperature, more electrons can go to the conduction band from the added impurity bands. Thus the conductivity of the extrinsic semiconductor increases. Extrinsic semiconductors are of two types-*N-type semiconductor* and *P-type semiconductor*.

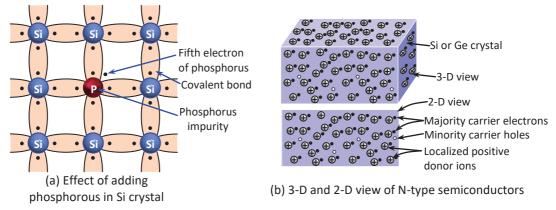

### N-type or Negative-type Semiconductor

Both the N-type and P-type semiconductor materials are formed by adding suitable impurity atoms into a pure semiconductor (Si, Ge, etc.). The N-type semiconductor is created by introducing elements that have five valence electrons (pentavalent elements), such as phosphorus, arsenic, antimony etc. The effect of the added impurity elements (phosphorus in silicon crystal) is depicted in Fig.2-3(a). There are five valence electrons at the outer most shell of phosphorus atoms. But four valence electrons form four covalent bonds with four adjacent silicon atoms. The fifth electron of

phosphorus atom remains unused. Every phosphorus atom added to the Si crystal has such an unused electron. These electrons are loosely bound to the parent atoms and can jump to the conduction band at room temperature and behave as *free electrons*. In this way, by adding suitable amount of pentavalent impurity atoms, the number of free electrons can be increased to a desired level. Now, as the crystal has many free electrons (negative charge), it is called *N-type semiconductor* (N for negative). The impurities with five valence electrons are called *donor atoms*.

Fig.2-3: Preparation of N-type semiconductor doping with pentavalent impurities

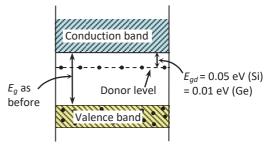

Note that a discrete energy level, called the **donor level**  $(E_{gd})$  is developed closed to the conduction band.  $E_{gd}$  (energy gap of donor level) is significantly less than that of the intrinsic material  $(E_g)$  as shown in Fig.2-3(c). Those unused electrons of the added impurity atoms can absorb sufficient thermal energy to move into the conduction band at room temperature. The result is that at room temperature, there are a large number of charge carriers (electrons) in the conduction

Fig.2-3(c) Energy band diagram of N-type semiconductor

band. So, the conductivity of the material increases significantly. Although, electrons are the majority charge carriers in N-type semiconductor, at room temperature some electrons move from the valence band to the conduction band and produce some holes in the valence band. These holes are called minority carries in N-type semiconductor.

In summary, we can say, an N-type semiconductor has electrons as majority carriers, and holes as minority carriers as shown in Fig.2-3(b). As every donor atom donates one electron, electrically it becomes positive. They cannot move and remain as *localized positive ions* in the crystal.

## P-type or Positive-type Semiconductor

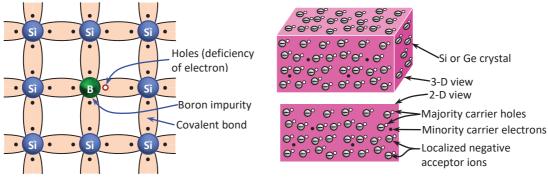

The P-type semiconductor material is developed in the same process. A pure germanium or silicon crystal is doped with impurity atoms having three valence electrons (i.e., trivalent impurities). Examples of such impurities are: boron (B), gallium (Ga), and indium (In) etc.

(a) Effect of adding boron in Si crystal

(b) 3-d and 2-d view of P-type semiconductors

Fig.2-4: Preparation of P-type semiconductor doping with trivalent impurities

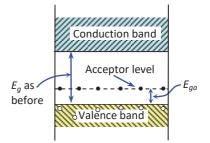

The effect of adding boron atoms in silicon is indicated in Fig.2-4(a). Three electrons of the outer most shell of boron form three covalent bonds with three adjacent Si atoms. But the fourth adjacent Si atom cannot form a complete covalent bond due to an electron deficiency. This deficiency of electron is called a *hole* and is represented by a circle or a plus sign. The holes behave like positive charge because they can capture electrons. Since, the trivalent impurities capture (accept) electrons, they are called *acceptor*. Every acceptor added in the silicon crystal

Fig.2-4(c): Energy band diagram of P-type semiconductor

introduces an energy state in the energy band diagram. This energy level is called *acceptor level*. The acceptor level is produced in between the conduction band and the valence band, close to the valence band [Fig.2-4(c)]. The energy difference between the valence band and the acceptor level ( $E_{ga}$ ) is very small. At room temperature, electrons can easily absorb sufficient heat energy and jump from the valence band to the acceptor level. The electrons that move to the acceptor level, leave behind holes in the valence band. Thus many holes are developed in the valence band. The holes are the majority charge carriers in P-type semiconductor. As in the case of intrinsic semiconductors, some electrons will absorb sufficient thermal energy and will jump from valence band to the conduction band. These electrons are called minority charge carriers.

In summary, we can say, a P-type semiconductor has holes as majority carriers, electrons as minority carriers and negatively charged localized acceptor ions as shown in Fig.2-4(b).

## 2.5 PN Junction Diode

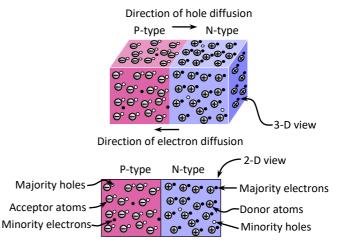

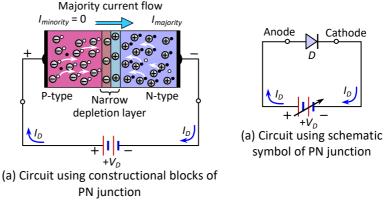

If one half of a semiconductor slab is made P-type and the other half is made N-type or some portion of a semiconductor is made P-type and the rest of it is made N-type, a PN junction will be developed (Fig.2-5). Some changes take place at the interface of P-type and N-type material and a depletion layer and a barrier voltage ( $V_B$ ) is developed.

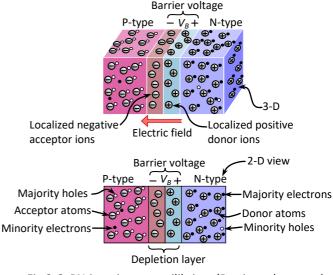

As shown in Fig.2-5 there are majority of holes in the P-type semiconductor and majority of electrons in the N-type semiconductor. Due this to concentration variation electrons diffuse from N-type to P-type and holes diffuse to N-type. If an electron comes to P-type material it will neutralize a hole, similarly if a hole moves to N-type it will neutralize an electron. In this way, a region will be developed that has no free carrier as shown in Fig.2-6. This region, at the interface of Ptype and N-type materials, is called depletion region or depletion layer

Fig.2-5: PN-junction before equilibrium

as the region has been depleted off free charge carriers.

Note that there are localized acceptor ions in the depletion layer of P-type and donor ions in the Ntype material. Since, acceptor ions are negative and the donor ions are positive, an *electric field* will be developed in the depletion layer and its direction will be from positive to negative, i.e., from Ntype to P-type as shown in Fig.2-6. The direction of the electric field will be such that it will oppose the diffusion of majority carriers. With the diffusion of more and more majority carriers, the strength of the electric field will gradually increase. At a certain value of electric field strength the diffusion of the majority carriers will stop and

we say that the PN junction has reached to *equilibrium*. In other way, we can say that, the negative ions in the P-type and the positive ions in the N-type will produce a potential difference. Actually this potential difference will produce the aforesaid electric field. As this potential difference opposes the flow of majority carriers, it is called *barrier voltage*  $V_B$ . For silicon PN junction, the typical value of the barrier voltage is  $\approx 0.7$  V and for germanium PN junction its value is  $\approx 0.3$  V.

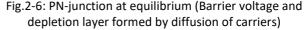

When metal contacts are made to the P-type and Ntype semiconductor, as shown in Fig.2-7, a PN *junction diode* or simply a semiconductor *diode* is produced. The electrical symbol of a diode is shown in the same figure. The terminal connected to Ptype material is called *anode* and that connected to N-type material terminal is called *cathode*. The arrow head indicates the direction of the conventional current flow as will be described later.

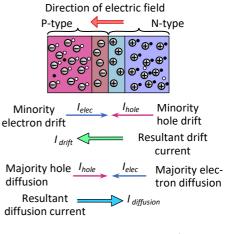

## 2.6 Current in PN Junction at Equilibrium

When the barrier voltage  $V_B$  of a PN junction becomes 0.7 V (for Si) or 0.3 V (for Ge) the diffusion of majority carriers stops and the junction comes to an electrical equilibrium condition. However, at room temperature, both the majority and minority carriers produce random motions. Hence,

if a minority carrier electron of P-type semiconductor comes within the depletion region (where the electric field exists), the electric field will push it to the N-side, called *drift current*. Similarly, the minority carriers of N-type material drift to the Pside. In this way, two drift currents will be produced (Fig.2-8). The two drift currents will add up and will produce a resultant *drift current* as shown in the figure.

As, due to the drift of minority carriers, the number of majority carriers has increased (both in P-side and N-side) than that without drift, hence, majority carrier hole will diffuse from P-type material to the N-type material and the majority carrier electrons will diffuse from N-type to P-type material. The two diffusion currents will also add up and will produce a

resultant current which is called *diffusion current*. As shown in Fig.2-8, at equilibrium condition, the magnitudes of the drift current and the diffusion current will be same, and the net resultant current through the PN-junction will be zero at equilibrium.

## 2.7 *I-V*Characteristic of a PN Junction Diode

*Biasing* is the process of applying an external potential (voltage) to a device. The voltage applied for biasing is called *bias voltage*. A PN junction can be biased in forward direction or in reverse direction.

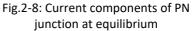

## **Characteristics in Reverse Biased Condition**

When an external potential (i.e., a battery) is connected across a PN junction diode with the positive terminal of the battery connected to the N-type material and the negative terminal connected to the P-type material as shown in Fig.2-9, the situation is called *reverse bias*. The

number of positive ions in N-type material of the depletion region will increase due to the large number of free electrons drawn by the positive terminal of the applied potential. For similar reasons, the number of negative ions will increase in the P-type material. The net effect, therefore, is that the width of the

Fig.2-9: Reverse biased PN junction diode

depletion region will increase. This widening of the depletion region will establish a greater barrier for the majority carriers reducing the majority carrier flow. The drift of the minority carriers, however, will continue. This results in a very small current from N-side to P-side.

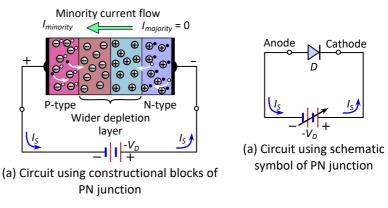

Fig.2-10: I-V Characteristic curve of a PN junction diode

The current that exists under reverse-bias condition is called the *reverse saturation current* (or *dark saturation current*) and is represented by  $I_s$  (Fig.2-10). The value of  $I_s$  depends on the temperature. At 25 °C the value of  $I_s$  of a low power diode is typically 1  $\mu$ A or less. For a very large value of reverse voltage, the reverse current increases suddenly and if the current is not controlled, the diode may be destroyed. The value of the reverse bias voltage for which the reverse current increases rapidly is called *reverse breakdown voltage*  $V_{BR}$  as shown in Fig.1-11.

### **Characteristics in Forward Biased Condition**

A forward bias is established by connecting the positive terminal of a battery to the P-type material and the negative terminal to the N-type material as shown in Fig.2-12. The application of a forward bias ( $V_D$ ) will pressure electrons in the N-type material and holes in the P-type material to recombine with the ions near the boundary and reduce the width of the depletion

region as shown in Fig.2-12. The applied voltage will almost completely drop across the depletion layer. This forward voltage will produce an electric field which is in the opposite direction of original electric field of the barrier voltage.

Thus, the resultant electric field will decrease and the current due to minority carriers (minority drift

Fig.2-12: Forward biased PN junction diode

current) will decrease and the majority current (diffuse current) will increase. If the applied forward bias voltage is equal to the barrier voltage ( $V_B$ ), the resultant field in the depletion layer will be zero. Now, the minority carrier current will be zero and the majority carrier current will be high. In the forward bias condition, therefore, the forward current increases rapidly when the applied voltage is near about the barrier voltage  $V_B$ . The point of the *I-V* curve where the forward current increases rapidly is called *knee point* (Fig.2-10). After the knee point the current will increase rapidly with a very small increase in the forward voltage.

From the theory of solid-state physics, the general characteristics of a semiconductor diode can be defined by the following equation (Equ.2-1). This equation is referred to as Shockley's equation.

$$I_D = I_S \left( e^{\frac{qV_D}{nkT}} - 1 \right) \tag{2-1}$$

$$I_D = I_S \left( e^{\frac{V_D}{nV_T}} - 1 \right)$$

(2-2)

where,  $I_s$  = reverse saturation current

q = magnitude of charge of an electron = 1.6  $\times 10^{-19}$  C

$V_D$  = applied forward bias voltage to the diode

n = diode ideality factor, which is a function of the operating conditions and physical construction; its value has the range between 1 and 2 depending on a wide variety of factors (for simplicity, we will consider n = 1 unless otherwise stated).

k = Boltzmann's constant = 1.38 × 10<sup>-23</sup> J/K T = Absolute temperature

$V_T = \frac{kT}{q}$ .  $V_T$  is called *thermal voltage*. At 27° C or 300 K the value of  $V_T$  is 26 mV.

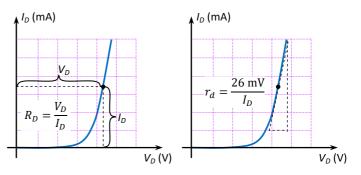

The DC resistance at any point of the input characteristics can be calculated using the following equation.

$$R_D = \frac{V_D}{I_D}$$

(2-3)

And, the AC resistance at any point can be calculated by using the following equation.

$$r_d = \frac{26 \text{ mV}}{I_D} + r_B \tag{2-4}$$

Here,  $r_B$  is the bulk resistance of the PN junction which is very low and can be neglected.

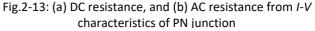

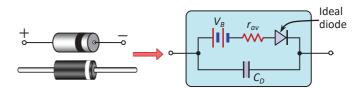

#### 2.8 Ideal Diode

In electronic circuits a PN junction diode is used as a switch that allows current only in one direction (forward direction). Although, a PN junction can behave as a one-way switch, in addition to switching property it has barrier voltage  $V_B$ , reverse saturation current  $I_S$ , junction capacitance ( $C_D$ ) and some resistances ( $R_D$ ). Actually these additional parameters are unwanted. An ideal diode is such a diode that provides only the one-way switching property, but will have no barrier voltage, reverse current, junction capacitance, and any resistance. Moreover, an ideal diode will have no limitation like – reverse breakdown, forward current limitation etc. The *I-V* characteristic curve of an ideal diode is given in Fig.2-14(a).

Fig.2-14: (a) Characteristics of an ideal diode, (b): Switch and ideal diode analogy

The operation of an ideal diode can be compared with that of a mechanical switch. If the diode is forward-biased, it works like a closed (ON) switch and if it is reverse-biased the diode works like an open (OFF) switch as shown in Fig.2-14(b). Though a mechanical switch can conducts current in both directions, a diode conducts current only in the forward direction.

#### 2.9 Diode Equivalent Circuit

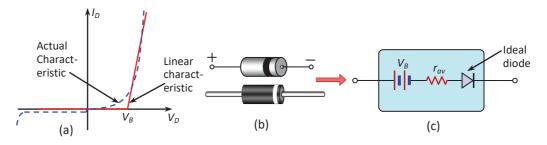

Neglecting the non-linearity of the characteristic curve, we can represent it by three straight lines [Fig.2-15(a)]. The equivalent circuit of the diode will be as shown in Fig.2-15(c). For this

characteristic, the equivalent circuit can be represented by a barrier voltage  $V_B$ , a resistance  $r_{av}$  and an ideal diode D connected in series as shown in Fig.2-15(c). Here,  $r_{av}$  is the average resistance of the portion of the characteristic curve after the knee point.

Fig.2-15: (a) Actual and linearized characteristics, (b) Actual diodes, and (c) Equivalent circuit of a diode

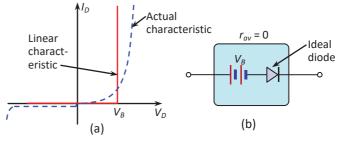

We know that the value of  $r_{av}$  is very small, typically less than 100  $\Omega$ . Hence in some operations, we can neglect this resistance. In that case, the equivalent circuit of the diode will consist of a barrier voltage  $V_B$ , and an ideal diode D connected in series as shown in Fig.2-16(b). The characteristic of this approximation will be as shown in Fig.2-16(a).

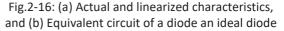

Even in some situations, where the external resistance is very high and the circuit operating voltage level is also very high compared to  $V_B$ , the operation of a practical diode can approximate to that of an ideal diode. Here, we neglect both  $r_{av}$  and  $V_B$ . The characteristic curve and the equivalent circuit are shown in Fig.2-17(a) and (b), respectively.

and (b) Equivalent circuit of a diode

In these three equivalent circuits, the capacitance effect of the diode has not been considered. That is, these three equivalent circuits are considered DC equivalent circuits.

### **Equivalent Circuit with Capacitance**

Every PN junction shows some capacitance effect ( $C_D$ ). The capacitance of a PN junction is so small that in normal operation we can neglect it. But the capacitance becomes effective in very high frequency operation. Considering the junction capacitance, the equivalent circuit will be as shown in Fig.2-18.

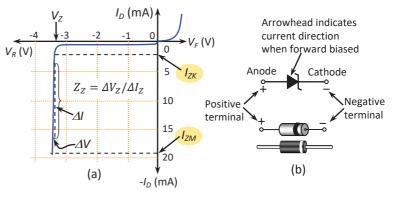

## 2.10 Zener Diode

For a very large reverse bias voltage of a diode, the reverse current rapidly increases from reverse saturation current (breakdown). This phenomenon is used to produce a constant voltage device, called **Zener diode**. There are two mechanisms that cause breakdown in reverse biased PN junction.

Fig. 2-18: AC equivalent circuit of a diode considering  $r_{av}$ and  $V_B$

#### Zener Breakdown Mechanism

This type of breakdown takes place in the PN junction where the doping concentration is very high. Due to the high doping concentration, the width of the depletion layer will be comparatively small. So, for a particular reverse bias voltage, the electric field strength  $[V_D/(\text{width of the depletion layer})]$  in the depletion layer, will be high enough to break away electrons from their atoms. With the breakdown of many such electrons insulating depletion layer converts into a conductor. This ionization by electric field is called **Zener breakdown** according to the name of its inventor. The Zener breakdown occurs usually with reverse bias voltage less than 5 V.

#### **Avalanche Breakdown Mechanism**

If the doping concentration of the PN junction is low the width of the depletion layer will be very large. So, when the reverse saturation current flows, the carriers travel a comparatively long distance and achieve large kinetic energies. If these energetic carriers collide with the electrons of covalent bonds of the crystal, the electrons become free. The newly developed free

Fig.2-19: (a) Zener diode characteristics, (b) Symbol and practical diodes.

electrons also collide with other atoms and produce more free electrons. In this way, the carrier concentration in the depletion layer increases and the reverse current increases rapidly resulting in the junction breakdown. This breakdown mechanism is called *avalanche breakdown*.

#### **Characteristics of Zener Diode**

Zener diode has almost the same characteristic as the normal low power rectifier diode except the lower value of reverse breakdown voltage. The typical characteristics of a Zener diode are shown in Fig.2-19(a) and the symbol of a Zener diode is shown in Fig.2-19(b).

In the reverse bias condition very small amount of reverse current flows. But after the Zener breakdown voltage  $V_{7}$ , the reverse current increases rapidly. The operating point of a Zener diode may lie at any point of the reverse characteristic curve after breakdown. The Zener diode is used in circuit to produce a constant voltage  $(V_z)$  and its

physical construction of LED using r v junction (b) ryph

performance depends on the shape of the reverse characteristics. The variation of this constant voltage with current depends on *dynamic impedance* of Zener diode ( $Z_z$ ) calculated as,

$$Z_Z = \frac{\Delta V_Z}{\Delta I_Z} \tag{2-5}$$

As illustrated in Fig.2-19(a)  $Z_Z$  defines how  $V_Z$  changes with the change of reverse current. The Zener diode current may be of any value between  $I_{ZK}$  and  $I_{ZM}$ . Here,  $I_{ZK}$  is the reverse current at the knee point of the reverse characteristic and  $I_{ZM}$  is the maximum Zener diode current which is limited by the power of a Zener diode.

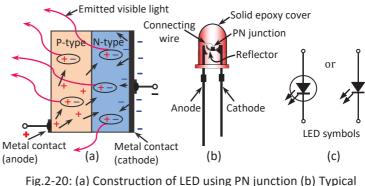

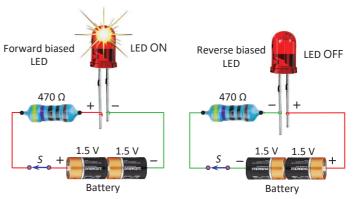

### 2.11 Light Emitting Diode

Light emitting diode (LED) is a very common optoelectronic device used as an indicating device, nowadays as light source (LED tube lights, LED bulbs etc.). LEDs are also used to manufacture today's very high quality televisions, computer monitors and mobile phone displays. LED is nothing but a PN junction of suitable (direct band-gap) semiconductor materials. In a forward biased PN junction, light is emitted when the free electrons recombine with holes.

A cross-sectional view of an LED junction is shown in Fig.2-20(a). Instead of using a single semiconductor, alloys like gallium arsenide (GaAs), gallium phosphide (GaP), gallium arsenide

phosphide (GaAsP) etc. are used for LED manufacturing. Combinations of different materials and ratio of different components produce different colors. To make an LED an Ntype epitaxial layer is grown upon a substrate, and the Pregion is created by diffusion method. The substrate is placed in a cup-type reflector that also works as the cathode connection as shown in Fig.2-20(b). The

Fig.2-21: LED produces light when forward biased

positive (anode) lead is connected to P-type material by a very narrow wire. The whole arrangement is encapsulated in an epoxy lens (plastic cover).

#### **Operation**

When an LED is forward biased with a suitable voltage (about 1.5 V or more), a forward current flows through it. Electrons flow from N-side to the P-side and recombine with holes which are the majority carriers of P-type materials. When the free electrons come back to valence band from conduction band they emit their extra energy which is equal to band-gap energy ( $E_g$ ). The extra energy is emitted as photons. By selecting suitable materials and changing their combination ration, band-gap energy ( $E_g$ ) is changed and light of different color is produced.

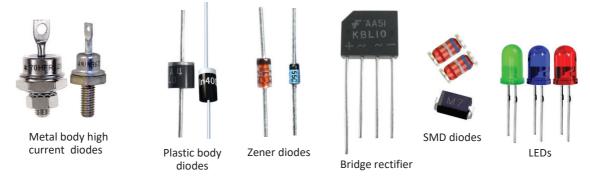

Fig.2-22: Photographs of different types of diodes

## 2.12 Applications of PN Junction Diodes

PN junction diodes are mainly used as rectifier, clipper circuits, clamper circuits etc. There are different types of rectifier circuits. Here, only two full wave rectifiers are described.

### **Full-Wave Rectifier**

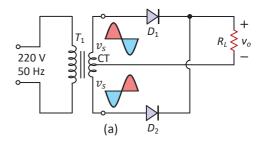

In *half-wave rectifier*, the load gets power only for one half-cycle of the input AC power. That's why it has low DC and RMS value. But in a *fullwave rectifier*, the load gets power for full-cycle of the input power. A full-wave rectifier with a centre-tapped transformer is shown in Fig.2.23. It uses two rectifier diodes and its input voltage is supplied from a transformer ( $T_1$ ). The transformer must have a tape at the centre (CT).

Fig.2-23: Two-diode full-wave rectifier

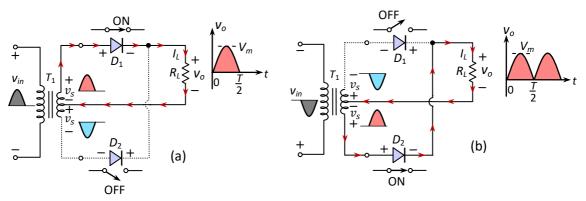

The function of the transformer is to step down 220 V AC power into required voltage, like 12 V, or 16 V etc. As shown in Fig.2-24(a), for the positive half cycle of input, the top-most terminal of centre-tapped transformer will be positive w.r.t. centre-tape, and the bottom-most terminal will be negative w.r.t. the centre-tape (at the secondary coil). For the negative half-cycle, the polarity will be just opposite [Fig.2-24(b)]. Both the secondary coils will produce same amount of AC voltage,  $v_s = V_m \sin(\omega t)$ .

Fig.2-24: (a) Circuit status for the positive half-cycle (b) Circuit status for the negative half-cycle

During the positive half-cycle (t = 0 to T/2), the transformer output voltage is positive at the top. This positive terminal is connected to the anode of  $D_1$ , and the negative centre-tape is connected to the cathode of  $D_1$  via  $R_L$ . Consequently,  $D_1$  is forward biased, and load current,  $I_L$ , flows from top of the transformer secondary through  $D_1$ , through  $R_L$  (downward), and back to the transformer centre-tap. During this time, the polarity of the voltage from the bottom half of the transformer secondary causes diode  $D_2$  to be reverse biased. Thus,  $D_1$  behaves as short-circuit (ON) and  $D_2$ behaves as open circuit (OFF) as shown in Fig.2-25(a). If the diode voltage drop is neglected the whole input voltage (transformer output voltage) will be developed across the load  $R_L$ .

During the negative half-cycle of the input (t = T/2 to T), the bottom-most terminal of the transformer secondary will be positive and the centre-tape will be negative. So,  $D_2$  will be forward biased and behaves as short circuit as illustrated in Fig.2-25(a). Now, the load current flows from bottom of the transformer secondary through  $D_2$ , through  $R_L$  (from top to bottom),

and back to the transformer centre-tape. As the polarity of the voltage of the upper half of the secondary has just reversed, diode  $D_1$  will now be reverse biased and it will behave as open circuit.

The direction of load current is always downward, that is, load is getting full-wave DC voltage. But the output is not pure DC, it is pulsating DC. If we neglect

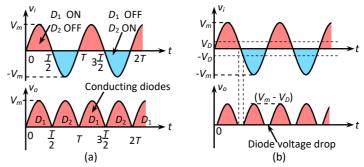

Fig.2-25: (a) Full-wave rectified output neglecting diode's barrier voltage  $V_D$ , and (b) Full-wave rectified output considering  $V_D$

the voltage drop of the diodes the output waveform will be as shown in Fig.2-25(a). But, if we consider the voltage drop of the diodes the output wave form will be as shown in Fig.2-25(b). For both the positive and negative half-cycles, the voltage dropped across the reverse biased diode will be  $2V_m$ . So, the PIV (*peak inverse voltage*) rating of the diodes must be greater than  $2V_m$ .

The average DC output voltage of the full-wave rectifier will be,

$$V_{dc} = V_{avg} = \frac{2V_m}{\pi} \text{ or } \frac{2(V_m - V_D)}{\pi}$$

(2-4)

And the RMS output voltage will be,

$$V_{rms} = \frac{V_m}{\sqrt{2}} \text{ or } \frac{(V_m - V_D)}{\sqrt{2}}$$

(2-5)

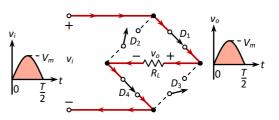

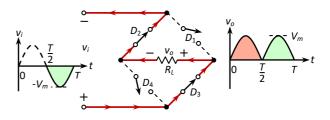

#### **Full-Wave Bridge Rectifier**

If the transformer does not have centre-tape then we have to use bridge rectifier circuit to get full-wave output.

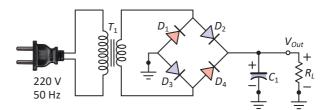

The circuit diagram of a bridge rectifier is shown in Fig.2-26.

The bridge rectifier consists of four diodes connected with their arrowhead symbols all pointing toward the positive output terminal of the circuit. Among the four corners of a bridge rectifier two are AC input terminals and two are DC output terminal. The points at which anode of one diode and the cathode  $v_i = v_m \sin(\omega t)$

Fig.2-26: Full-wave bridge rectifier

Fig.2-27: Circuit status for the positive half-cycle of input AC voltage

of one diode are connected are AC input terminals (marked by ' $\sim$ '). The terminal where the cathodes of two diodes are connected is the positive terminal of DC output (marked by '+'), and

the point at which the anodes of two diodes are connected is the negative output terminal ('-').

During the positive half-cycle of input voltage, diodes  $D_1$  and  $D_4$  become forward bias and conducts current (Fig.2-27). During the negative half-cycle of the input, diodes  $D_2$  and  $D_3$  are forward biased and conducts current (Fig.2-28). The output waveforms will be exactly same as the first rectifier and the same

Fig.2-28: Circuit status for the negative half-cycle of input voltage

equations can be used. But the voltage drop will be double  $(2V_D = 1.4 \text{ V})$  as the current passes through two diodes. Hence,  $V_{dc} = V_{avg} = 2(V_m - 2V_D)/\pi$ , and  $V_{rms} = (V_m - 2V_D)/\sqrt{2}$ .

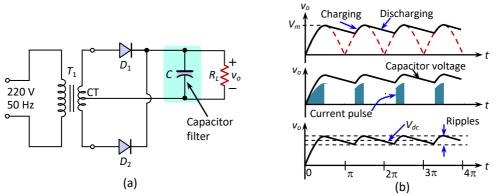

#### 2.13 Filters

In general a *filter* is a circuit that blocks a particular range of frequencies and passes other range of frequencies. In case of rectifier, the function of the filter circuit is to block the AC voltage and to pass the DC voltage to the load. There are different types of filter circuits. Here, the shunt capacitor filter is discussed.

As shown in Fig.2-29(a), a capacitor (*C*) connected at the output terminal across the load resistor ( $R_L$ ) works as a good filter. For the positive half-cycle diode  $D_1$  is forward biased and the capacitor is charged quickly to the peak value of input voltage,  $V_m$ . When the output voltage of the rectifier decreases from the peak value, the stored peak voltage of the capacitor reverse biases the diode,  $D_1$ . Now, the capacitor discharges through the load resistance  $R_L$ . Hence, the voltage decreases gradually. During the negative half-cycle,  $D_2$  becomes forward biased and charges the capacitor to  $V_m$  voltage again. The process is continued and the output voltage across the load becomes smoother than the pulsating waveform. The output waveforms are shown in Fig.2-29(b).

Fig.2-29: (a) Full-wave rectifier with capacitor filter, (b) Output waveform with capacitor filter

With the filter capacitor, the DC output voltage of this full-wave rectifier circuit will be,

$$V_{dc} = V_m \times \left(\frac{2fCR_L}{1 + 2fCR_L}\right) \tag{2-6}$$

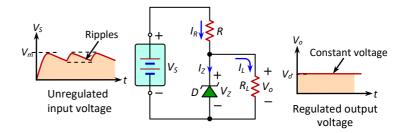

## 2.14 Voltage Regulator Using Zener Diode

The output voltage of the power supplies described above (consisting of a transformer, a rectifier circuit, and a filter circuit) may vary due to the change of AC supply voltage and the load resistance. This variation can be reduced by using a *regulator* at the final stage (in between filter and the load). Although a lot of complicated circuits are employed as voltage regulator (discussed

in Chapter 9), for a low power application Zener diode is commonly used. A simple regulator consists of a Zener diode and a series resistor as shown in Fig.2-30. The unregulated voltage ( $V_s$ ) is applied to the input of the circuit and the regulated output voltage ( $V_o$ ) is taken

Fig.2-30: Application of Zener diode as voltage regulator

across the Zener diode. The regulated output voltage will be equal to the Zener breakdown voltage  $V_z$ . The circuit will work properly if  $V_s > V_o$ . Resistor *R* limits the Zener diode current to the desired level and also drops the extra voltage ( $V_R = V_s - V_o$ ).

If the value of  $V_s$  increases the value of  $I_z$  increases and the voltage drop across  $R(V_R)$  increases, but  $V_o$  remains constant. Similarly, if  $V_s$  decreases,  $I_z$  decreases and the voltage drop  $V_R$  decreases and  $V_o$  remains constant again. On the other hand, if a load resistance is connected across the Zener diode, some current will be diverted from the Zener diode to the load. But the current through the resistor and hence voltage drop  $V_R$  will remain unchanged and so does the  $V_o$ . The value of  $I_z$  has to be set to a suitable level [in between  $I_{ZK}$  and  $I_{ZM}$  as shown in Fig.2-19(a)].

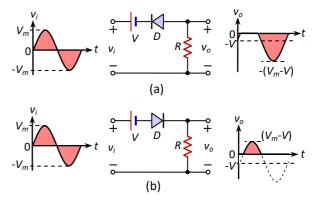

## 2.15 Clipper Circuits

*Clippers* are one kind of electronic networks or circuits that clip off a portion of an input signal without distorting the remaining part of the signal. Clipper circuits are made using diodes and resistors and sometimes a voltage source. Depending on the orientation of the diode, the positive or negative portion of the applied signal is clipped off. So, there are two types of clippers: positive and negative clipper circuits. *Positive clippers* remove the positive portion of the applied signal and pass the negative portion. On the other hand, the *negative clipper* clips the negative portion of the applied waveform and keeps the remaining region as original one. Although, an unbiased clipper clips a complete half-cycle, by using suitable bias to the diodes, less than or more that one half-cycle can be clipped off.

Depending on the position of the diode, clippers are also called either series clipper or parallel clipper. In *series clipper*, the diode is placed in series with the load resistance. But in *parallel clipper*, the diode is connected in parallel with the load.

Fig.2-31 shows a *biased series positive clipper* and a *biased series negative clipper* circuit. Here, we will consider  $0 < V < V_m$  and an ideal diode. Look at the polarity of the bias voltage (V). In the first circuit, it makes the diode forward biased, [Fig.2-31(a)]. Hence, even for no input voltage, that is, if the input terminals are short, the diode is still forward biased and -V amount of voltage will be available at the output. That's why the output waveform starts from -V volt. For the positive half-cycle of  $v_i$ , the forward bias voltage of the

Fig.2-31: (a) Biased series positive clipper circuit, (b) Biased series negative clipper circuit

diode (that was effective for V voltage) will gradually decrease. It will be clear if we look at the polarity of the positive half-cycle and the polarity of bias voltage (they oppose each other). For this reason, the output negative voltage will gradually decrease. When the value of  $v_i$  is equal to bias voltage V, the resultant voltage across the diode will be zero, and hence the diode will not conduct any current through the load, and hence, the output voltage will be zero as shown in

Fig.2-31(a). If the value of  $v_i$  exceeds V, the diode will be reverse biased by  $(v_i - V)$  volts, and no output again. Thus, the output will be zero as long as  $v_i > V$ . During the falling edge of the positive half-cycle when  $v_i = V$  the diode starts to conduct again, so we will get negative output voltage. During the negative half-cycle of the input,  $v_i$  will be added with V and forward bias the diode. Thus negative output will be available across the load from  $v_i = V$  up to  $v_i = -V_m$ . For this reason the negative peak will be  $-V_m - V = -(V_m + V)$ , which is shown in output waveform of Fig.2-31(a).

In the 2<sup>nd</sup> circuit, the direction of the diode is just opposite. So the bias voltage (V) will reverse biases the diode. The diode will block the negative voltage and pass the positive voltage. But due to the reverse bias voltage, V, the full positive half-cycle will not be found at the output. The maximum output voltage will be only  $V_m - V$  as shown in Fig.2-31(b).

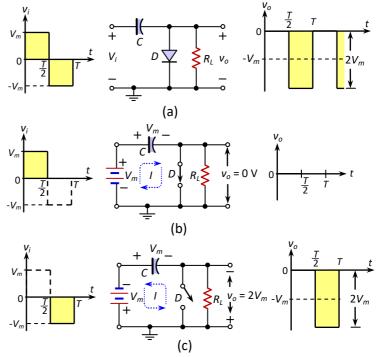

## **2.16 Clamper Circuits**

A *clamper* circuit, constructed of a diode, a resistor, and a capacitor, shifts a waveform to a different DC level without changing the shape of the signal. That is, a clamper circuit adds a DC level in the output signal. Depending on the direction of shifting, clamper circuits are classified as: *positive clampers* and *negative clampers*. Both of them may be either biased or unbiased. Thus, there are four types of

clampers:

- 1. Simple negative clamper

- 2. Simple positive clamper

- 3. Biased negative clamper

- 4. Biased positive clamper

## **Simple Negative Clamper**

The circuit diagram of a simple negative clamper is shown in Fig.2-32(a). To easily understand the operation of any clamper circuits, first we have to consider the half-cycle that forward biases the diode. Here, for the positive halfcycle of the input signal  $(0 \rightarrow \frac{T}{2})$ , the diode will be forward biased and the capacitor will be charged by  $V_m$  with +ve on the left side as shown in Fig.2-32(b). As the

Fig.2-32: (a) Negative clamper circuit (unbiased), (b) Operation for positive half-cycle, and (c) Operation for negative half-cycle

diode is short (neglecting barrier voltage), the voltage across the load resistance will be zero. However, during the negative half-cycle  $\left(\frac{T}{2} \rightarrow T\right)$ , the diode is reverse biased. So it will behave as an open circuit as shown in Fig2-32(c). For this situation, the value of output voltage can be obtained using KVL as,

$$-V_m - V_m + v_o = 0 \quad \therefore v_o = 2V_m$$

That is, the output voltage will be the sum of the capacitor voltage and source voltage with positive at the bottom. Thus, we will get  $v_o = -2V_m$ . Observe that, the input signal has been shifted to negative direction by a value of  $V_m$ . Or we can say a DC value of  $-V_m$  has been added to the output waveform.

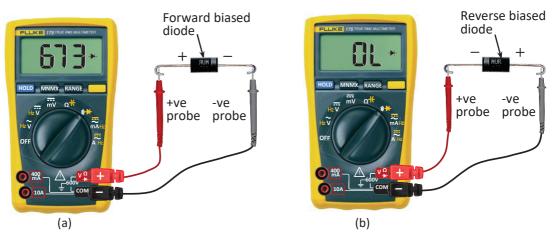

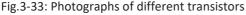

## 2.17 Testing Diode Using Multimeter

Sometimes it is necessary to test a diode to confirm whether it is OK or not. Using multimeter, we can do that. There are two ways to test a diode. We can use 'Diode Test' mode (shown by a diode symbol on the meter) of the multimeter, or if the multimeter has no 'Diode Test' option, we can use 'Resistance Test' option (shown by the ohm symbol). Here only the first method is discussed.

If we want to test a diode that is already connected in a circuit, we have to disconnect it, or disconnect at least one terminal of the diode from the circuit. For safety, the power supply of the circuit must be switched OFF. Moreover, we have to be careful about the high voltage stored in the capacitors or inductors!

As shown in Fig.2-33, the selector knob of the multimeter has to be set on 'Diode Test' position (indicated by a diode symbol). A good forward-based diode displays a voltage ranging from 500 mV to 800 mV for Si diode. But for germanium diodes the voltage range should be 200 mV to 300 mV. On the other hand, a reverse biased diode will show 'OL' reading. If the diode is not OK, it may be *short* or *open*. An open diode will also give 'OL' reading for both forward bias and reverse biase conditions. On the other hand, a short diode may give 0 V or very small voltage (300 mV for Si) in both directions.

Fig.2-33: (a) Forward bias testing, and (b) Reverse bias testing using multimeter

## **Bipolar Junction Transistor (BJT)**

## **3.1 Introduction**

In electronics, transistor is the most widely used device. The transistor was invented on December 23, 1947 at Bell Laboratories by William Shockley, John Bardeen and Walter Brattain<sup>[1]</sup>. Since then the applications of transistors are gradually increasing either in discrete form or in IC (Integrated Circuit) form. This chapter will discuss the construction and operations of transistors.

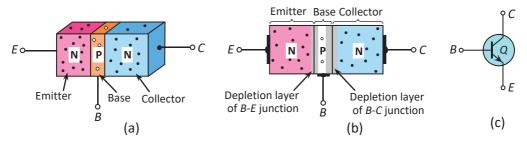

## 3.2 Construction of a Transistor

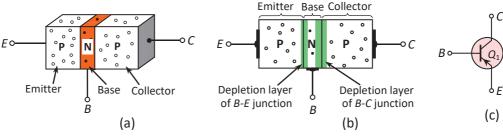

A bipolar junction transistor (simply called transistor) consists of two back-to-back PN junctions manufactured in a single piece of semiconductor material. It is constructed by sandwiching a P layer in between two N-layers as shown in Fig.3-1. This type of transistor is called an *NPN transistor*. Alternately, a transistor can be manufactured by sandwiching an N-layer in between two P-layers as in Fig.3-2. This configuration is called a *PNP transistor*.

The middle layer is called the **base** (B), of the remaining two layers one is called the **emitter** (E) and the other is called the **collector** (C). Terminal leads are attached to each layer of the transistor. The emitter and collecter layers are heavily doped (concentration of impurity atoms is high), but the base layer is lightly doped (concentration of impurity atoms is low). The outer layers have widths much greater than the sandwiched P or N-type layer. The actual dimension of transistor may vary from 10 to several 10s of microns. The doping of the sandwiched layer is also considerably less than that of the outer layers (typically, 1:10 or less).

Fig.3-1: Construction of NPN transistors, (a) Three-dimensional block, (b) Twodimensional block, and (c) Symbol of an NPN transistor

Fig.3-2: Construction of PNP transistor, (a) Three-dimensional block, (b) Twodimensional block, and (c) Symbol of a PNP transistor

Fig.3-1 and Fig.3-2 show the block diagrams and symbols of NPN, and PNP transistors, respectively. Look at the symbols of the transistors. The base terminal is in the middle and the collector and the emitter are connected to the base. Emitter is differentiated from the collector by an arrow. In NPN transistor the arrow direction is outward from the base and in PNP transistor the direction of the arrow is towards to base. This arrow direction indicates the direction of conventional current in the emitter terminal.

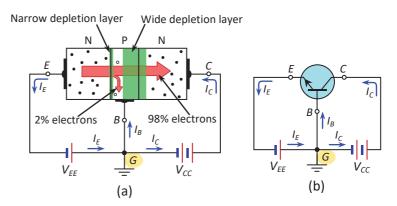

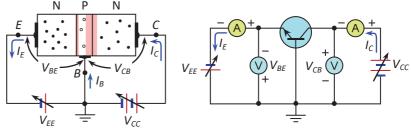

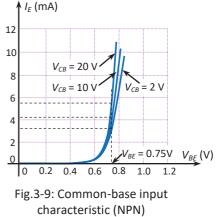

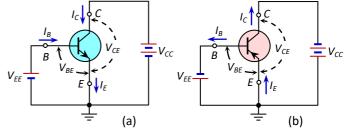

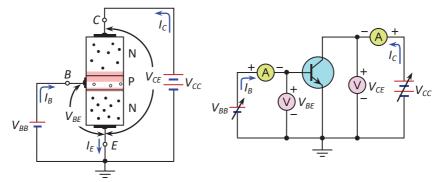

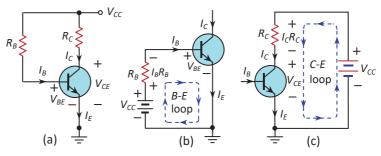

# **3.3** Operation of a Transistor

Here, the operation of an NPN transistor is described [Fig.3-3(a)]. For proper functioning of a transistor, the base-emitter junction (*B-E* junction) must be forward biased and the base-collector junction (*B-C* junction) must be reverse biased as shown in Fig.3-3. So, the negative voltage to the emitter and the positive

Fig.3-3: Operation of an NPN transistor, (a) Circuit with transistor block, and (b) Circuit with transistor symbol

voltage to the collector have been supplied with respect to the base. The base is common to

both the input circuit (*B*-*E* circuit) and the output circuit (*B*-*C* circuit), hence this configuration is called *common base configuration* (CBC).

Due to the forward bias, the depletion layer of *B-E* junction is reduced, that results in a heavy flow of majority carriers electrons from N-type emitter to P-type base material. These injected electrons are the minority carriers in P-type base. Due to the reverse bias, the depletion layer of the *B-C* junction is widened. The electric field of reverse biased *B-C* junction attracts the electrons injected by the emitter (which are the minority carriers in base region) and most of them manage to reach the collector layer. As the base is lightly doped and its width is very small, only a few of the electrons recombine with the majority holes in the base. For example, if 100 electrons are injected by the emitter per second, less than 2 electrons will recombine in the base and more than 98 will move to the collector. The direction of conventional current is just opposite to the direction of electrons flow. So, a current will be produced from emitter to battery which is called emitter current  $I_E$ . Due to the recombination of 2 holes (with 2 electrons) a small base current

$(I_B)$  will flow into the base. On the other hand, 98 electrons that move to the collector, constitute the injected collector current  $I_{C(INJ)}$  and its direction is from the battery to the collector as shown in Fig.3-3. Now, if we apply KCL at point G, we have

$$I_E = I_{C(INJ)} + I_B \tag{3-1}$$

From this operation it is now clear that more that 98% of the emitter current is transferred to the collector and only less than 2% is lost in the base. This current transfer action is called

Fig.3-4: Collector leakage current with emitter open

the *transistor action*. Due to the forward bias, *B-E* circuit has very low resistance and due to the reverse bias the *B-C* circuit has very high resistance. But the transistor has transferred the current from the low resistance circuit to the high resistance circuit. That is why, this device is called "*trans*fer-re*sistor*" or "*transistor*". The ratio of the injected collector current to the emitter current is called the *current gain* ( $\alpha$ ) of a transistor in common base configuration (CBC). That is,

$$\alpha = \frac{I_{C(INJ)}}{I_E}$$

$$I_{C(INJ)} = \alpha I_E$$

(3-2)

(3-3)

or,

...

The value of  $\alpha$  is less than unity and ranges from 0.95 to 0.997.

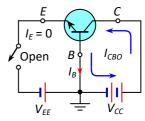

The  $I_{C(INJ)}$  is not only the current component in the collector. In the reverse bias *B*-*C* junction a leakage current flows due to the thermally generated minority carriers even if the emitter terminal is open (shown in Fig.3-4.). This current is denoted as  $I_{CBO}$ , *C*ollector to *B* as current with emitter *O*pen. Thus, the collector current  $I_C$  will have two components as,

$$I_C = I_{C(INJ)} + I_{CBO}$$

(3-4)

or,  $I_{C(INJ)} = I_C - I_{CBO}$

$$\alpha = \frac{I_C(INJ)}{I_E} = \frac{I_C - I_{CBO}}{I_E}$$

(3-5)

But as the value of  $I_{CBO}$  is very small it can be neglected, that is  $I_C = I_{C(INJ)}$ .

Therefore we can write

$$\alpha = \frac{I_{C(INJ)}}{I_E} \approx \frac{I_C}{I_E}$$

(3-6)

Using Equ.(3-4) and (3-6), we can also write,

$$I_C = \alpha I_E + I_{CBO}$$

(3-7)

Again, if we apply KCL at point G, we get,

$$I_E = I_C + I_B \tag{3-8}$$

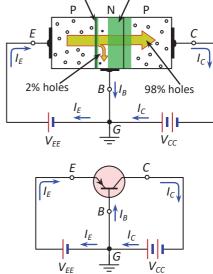

Operation of a PNP transistor is exactly same, except here holes move from emitter to collector through base, instead of electrons. The biasing voltages of the PNP transistor will also be in reverse direction as shown in Fig.3-5.

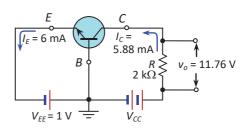

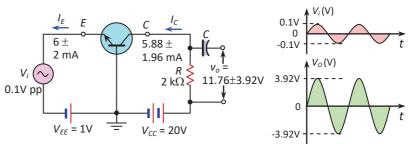

## 3.4 Amplifying Action of a Transistor

The capacity of a transistor to transfer a signal from a low resistance circuit to a high resistance circuit is the key factor for voltage amplification. As shown in Fig.3-6, even if we connect a large resistor, R, (say 2 k $\Omega$ ) at the collector circuit, transistor action will not be hampered, i.e., more than 98% of the emitter current will be transferred to the collector. Now let us consider that the emitter bias voltage  $V_{EE} = 1$  V and the forward resistance of the *B-E* junction is  $r_{in} = 50 \ \Omega$ . So in the emitter circuit  $I_E$  will be, Narrow depletion layer Wide depletion layer

Fig.3-5: Operation of a PNP transistor

Fig.3-6: Amplifying action of transistor

$$(V_{EE} - V_{BE}) \div r_{in} = (1 \text{ V} - 0.7 \text{ V}) \div 50 \Omega = 6 \text{ mA}$$

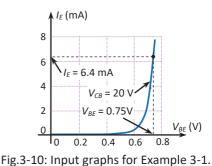

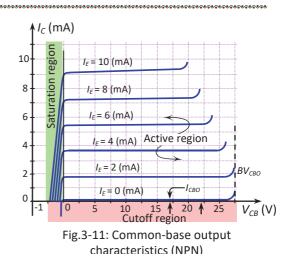

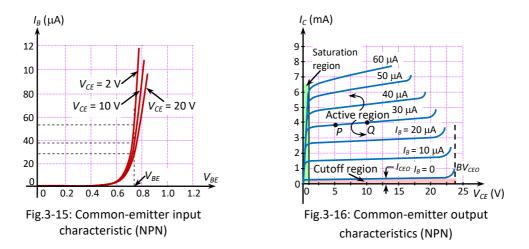

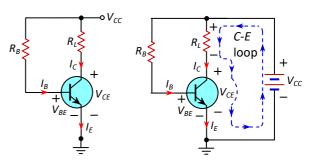

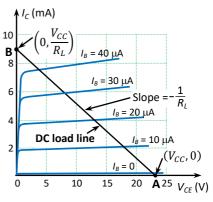

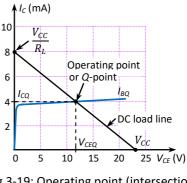

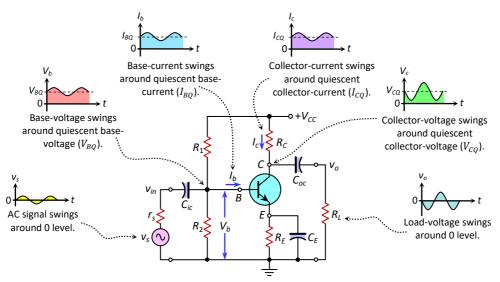

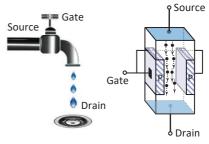

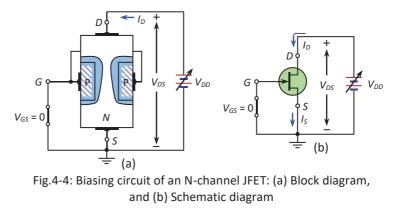

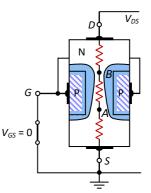

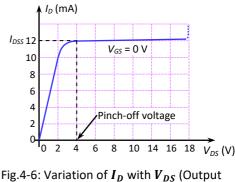

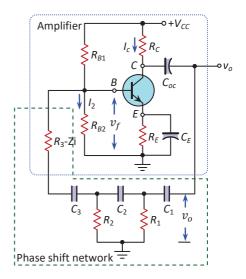

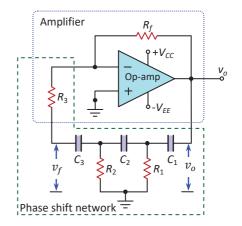

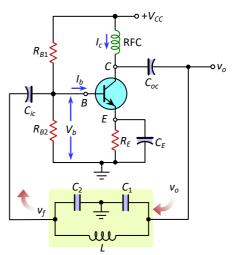

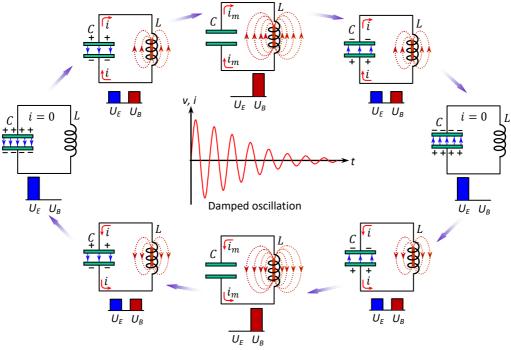

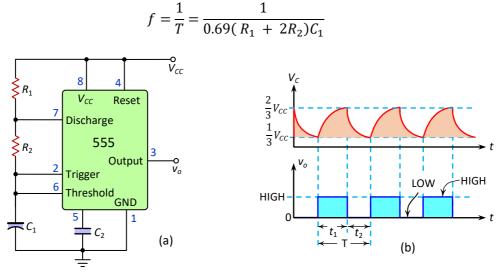

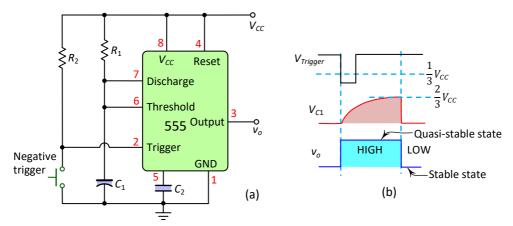

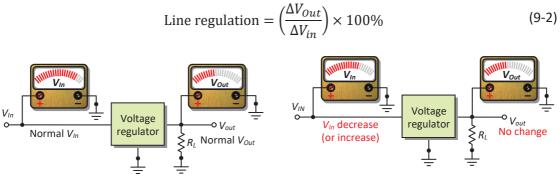

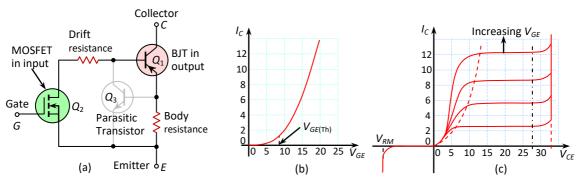

Due to the transistor action 98% of this current will be transferred to the collector. So,  $I_c$  will be 5.88 mA. If we take the output voltage ( $V_o$ ) across the external resistor R, according to Ohm's law its value will be 5.88 mA × 2 k $\Omega$  =